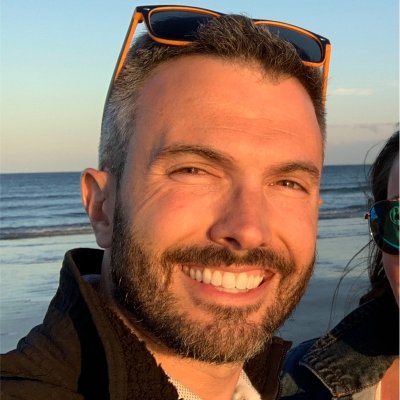

Tim Stratz serves as a Senior Manager of Custom Circuits Layout at Marvell Technology, where he leverages his extensive expertise in physical design layout to drive innovation in semiconductor technology. With a robust background in analog and custom digital layout creation, Tim has successfully navigated...

Tim Stratz serves as a Senior Manager of Custom Circuits Layout at Marvell Technology, where he leverages his extensive expertise in physical design layout to drive innovation in semiconductor technology. With a robust background in analog and custom digital layout creation, Tim has successfully navigated the complexities of various process nodes, including cutting-edge technologies down to 2nm. His proficiency in industry-standard tools such as Cadence Virtuoso, along with his adeptness in performing LVS (Layout Versus Schematic) and DRC (Design Rule Check), positions him as a pivotal figure in ensuring design integrity and performance optimization.

At Marvell, Tim is currently spearheading key projects that focus on enhancing the efficiency and reliability of ASIC designs. His leadership in managing cross-functional teams has been instrumental in streamlining workflows and fostering collaboration among engineers, thereby accelerating project timelines and improving overall output quality. Tim's deep understanding of EM/IR (Electromigration/IR Drop) analysis further enhances his capability to deliver robust layouts that meet stringent performance criteria.

In addition to his technical acumen, Tim is committed to mentoring emerging talent within the organization, sharing his insights on best practices in semiconductor layout design. His strategic vision and management skills not only contribute to the success of Marvell’s projects but also position the company at the forefront of semiconductor innovation. As the industry continues to evolve, Tim Stratz remains dedicated to pushing the boundaries of what is possible in custom circuit layout, ensuring that Marvell Technology remains a leader in the semiconductor space.